NDP6030PL

Description

These P-Channel logic level enhancement mode power field effect transistors are produced using Fairchild's proprietary, high cell density, DMOS technology. This very high density process is especially tailored to minimize on-state resistance.

Key Features

- RDS(ON) = 0.042 Ω @ VGS= -4.5 V RDS(ON) = 0.025 Ω @ VGS= -10 V

- Critical DC electrical parameters specified at elevated temperature

- Rugged internal source-drain diode can eliminate the need for an external Zener diode transient suppressor

- High density cell design for extremely low RDS(ON)

- 175°C maximum junction temperature rating

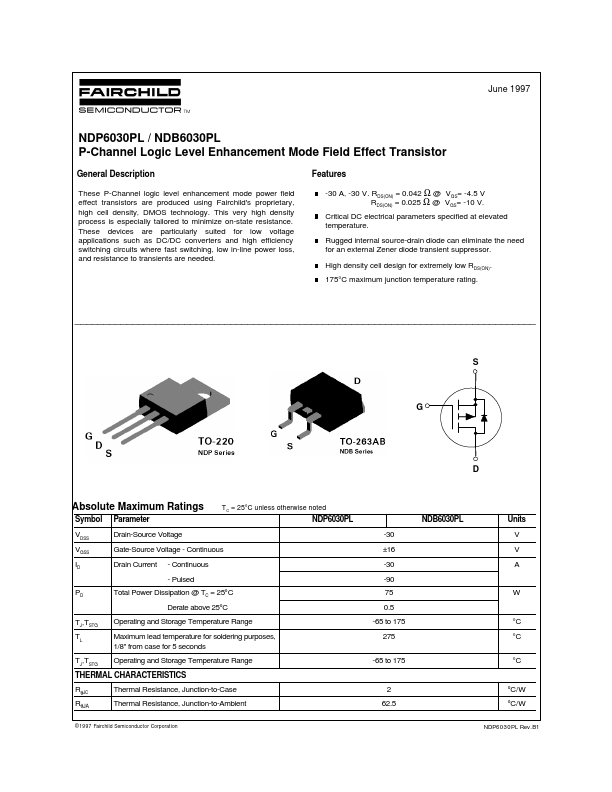

- ________________________________________________________________________________ S G D