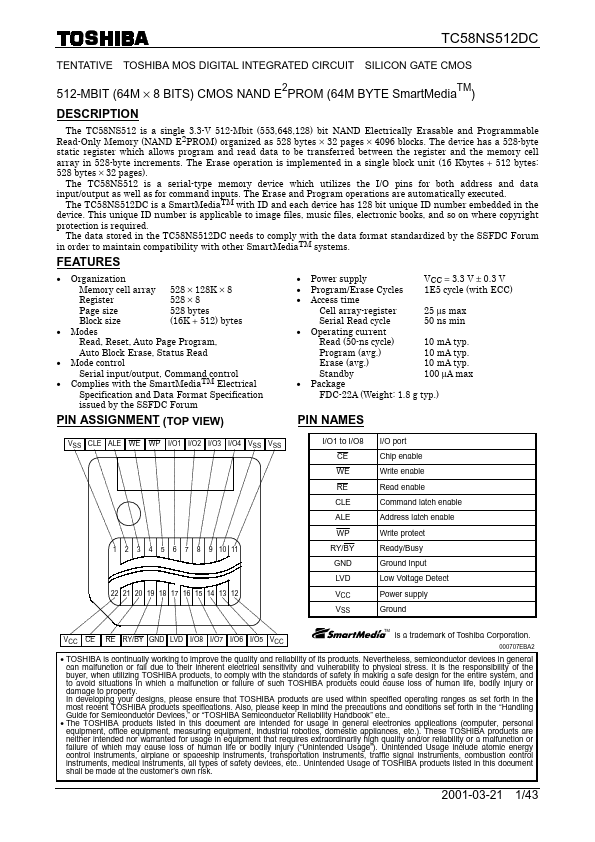

TC58NS512DC Description

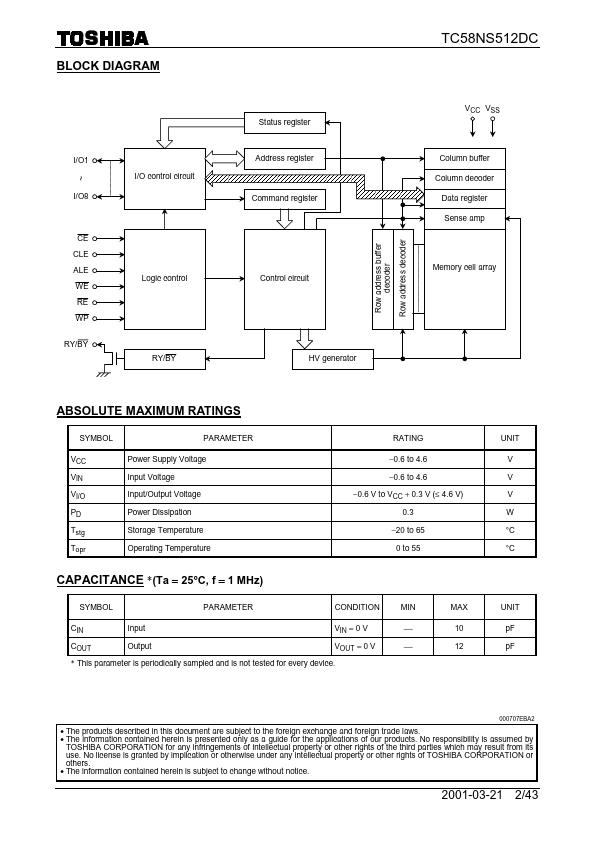

The device has a 528-byte static register which allows program and read data to be transferred between the register and the memory cell array in 528-byte increments. The Erase operation is implemented in a single block unit (16 Kbytes + 512 bytes: The TC58NS512 is a serial-type memory device which utilizes the I/O pins for both address and data input/output as well as for mand inputs.

TC58NS512DC Key Features

- Organization Memory cell array 528 × 128K × 8 Register 528 × 8 Page size 528 bytes Block size (16K + 512) bytes Modes Re

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devic