Datasheet Details

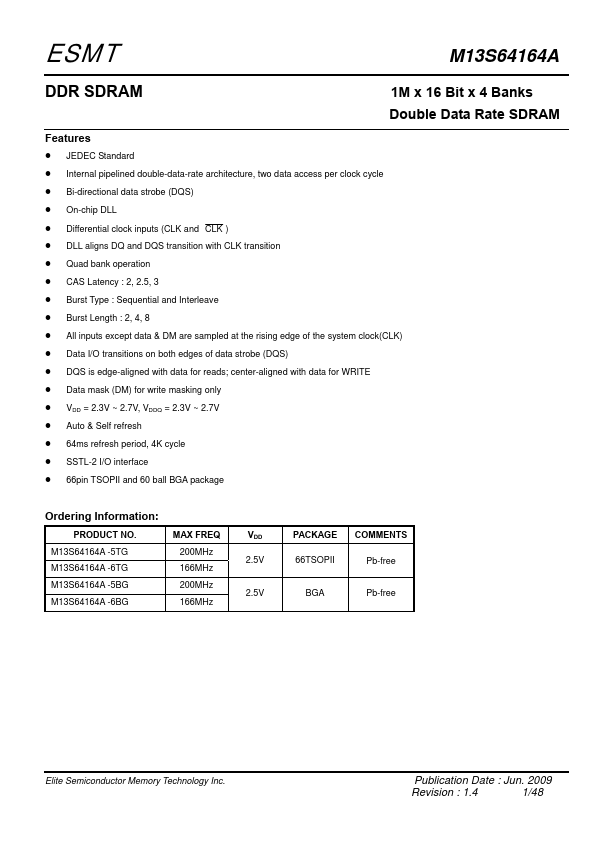

| Part number | M13S64164A-6TG, M13S64164A-5TG |

|---|---|

| Manufacturer | ESMT |

| File Size | 1.51 MB |

| Description | 1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| Datasheet |

|

| Note |

This datasheet PDF includes multiple part numbers: M13S64164A-6TG, M13S64164A-5TG. Please refer to the document for exact specifications by model. |